Just kinda thinking out loud here, don't have a solution or architecture in mind: I really want a better solution for high speed FPGA / ASIC protocol design and debug.

In particular:

1) Using scopehal protocol captures as stimuli for a virtual DUT (i.e. decoded 8b10b of PCIe or something into RTL simulator, pretending to be a SERDES)

TurboFuzz: FPGA Accelerated Hardware Fuzzing for Processor Agile Verification

Yang Zhong, Haoran Wu, Xueqi Li, Sa Wang, David Boland, Yungang Bao, Kan Shi

https://arxiv.org/abs/2509.10400

High-Parallel FPGA-Based Discrete Simulated Bifurcation for Large-Scale Optimization

Fabrizio Orlando, Deborah Volpe, Giacomo Orlandi, Mariagrazia Graziano, Fabrizio Riente, Marco Vacca

https://arxiv.org/abs/2510.12407

Low Latency, High Bandwidth Streaming of Experimental Data with EJFAT

Ilya Baldin, Michael Goodrich, Vardan Gyurjyan, Graham Heyes, Derek Howard, Yatish Kumar, David Lawrence, Brad Sawatzky, Stacey Sheldon, Carl Timmer

https://arxiv.org/abs/2510.12597

anybody doing Advent of FPGA in Amaranth? https://blog.janestreet.com/advent-of-fpga-challenge-2025/

it seems fun, and, moreover, if you have feedback as a learner I will be more than happy to use it to improve the language

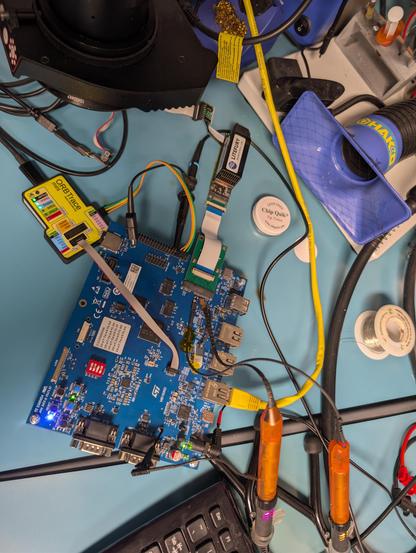

PCIe update: I'm now able to parse incoming InitFC1-* DLLPs and store away the credit counts in a register (which I don't actually use for anything yet), and emit a singular InitFC1-P DLLP of my own

Next step will be writing the rest of the setup logic so I can actually fully bring up VC0, then start sending UpdateFC idle DLLPs at regular intervals to keep the link alive when I'm not sending traffic.

ISAAC: Intelligent, Scalable, Agile, and Accelerated CPU Verification via LLM-aided FPGA Parallelism

Jialin Sun, Yuchen Hu, Dean You, Yushu Du, Hui Wang, Xinwei Fang, Weiwei Shan, Nan Guan, Zhe Jiang

https://arxiv.org/abs/2510.10225

Optimised neural networks for online processing of ATLAS calorimeter data on FPGAs

Georges Aad, Raphael Bertrand, Lauri Laatu, Emmanuel Monnier, Arno Straessner, Nairit Sur, Johann C. Voigt

https://arxiv.org/abs/2510.11469

Does anyone (maybe @… ) have any archival info on DINI Group FPGA boards?

I'm particularly interested in their very silly codenames. The main company front page is available on the wayback machine but since being acquired by Synopsys in 2019 it's no longer around and the wayback machine doesn't seem to have crawled most of their product…

I have an FPGA connected to the STM32 devkit now!

Minimum viable PCIe gateware any% gogogoo

A Scalable FPGA Architecture With Adaptive Memory Utilization for GEMM-Based Operations

Anastasios Petropoulos, Theodore Antonakopoulos

https://arxiv.org/abs/2510.08137 https://…

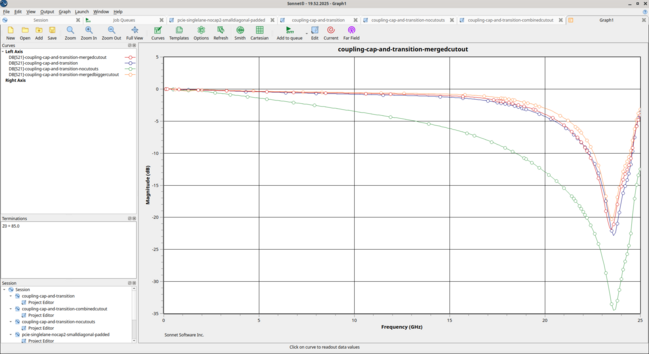

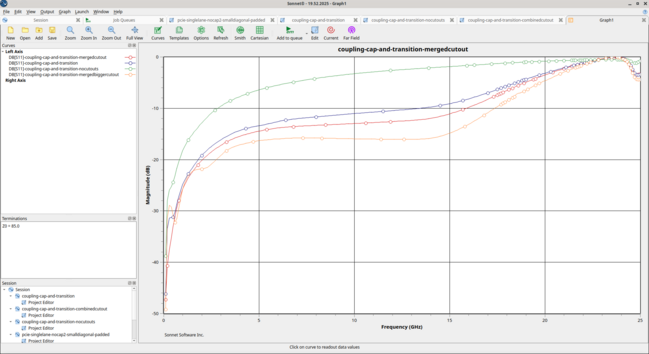

Checking on the Ceres FPGA board sims for @… that I had running while I was away. We're looking at a PCIe differential pair layer transition plus AC coupling capacitor.

With no cutout (green trace) response is awful: -3 dB insertion loss at 9.1 GHz, and -10 dB return loss at only 2.8 GHz.

Adding the cutout in the gerbers (blue trace) ma…

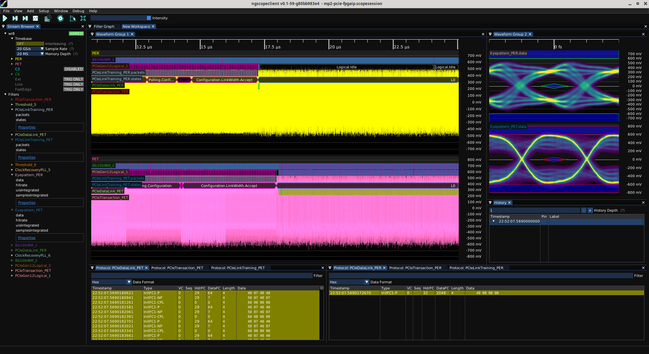

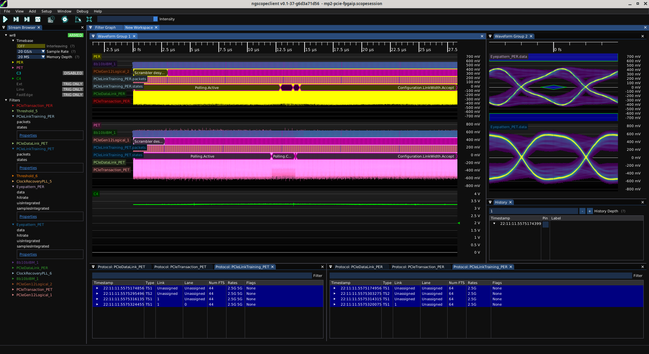

PCIe any% speedrun update: LTSSM is in full swing, I've made it all the way to Configuration.LinkWidth.Accept (and improved the ngscopeclient decode for link training in the process).

Enabling Time-Aware Priority Traffic Management over Distributed FPGA Nodes

Alberto Scionti, Paolo Savio, Francesco Lubrano, Federico Stirano, Antonino Nespola, Olivier Terzo, Corrado De Sio, Luca Sterpone

https://arxiv.org/abs/2509.26043

The MISTer FPGA is overrated crap

always_comm: An FPGA-based Hardware Accelerator for Audio/Video Compression and Transmission

Rishab Parthasarathy, Akshay Attaluri, Gilford Ting

https://arxiv.org/abs/2509.11503

Design and deployment of a fast neural network for measuring the properties of muons originating from displaced vertices in the CMS Endcap Muon Track Finder

Efe Yigitbasi (on behalf of CMS Collaboration)

https://arxiv.org/abs/2509.21062

Development of Deep Neural Network First-Level Hardware Track Trigger for the Belle II Experiment

Y. -X. Liu, T. Koga, H. Bae, Y. Yang, C. Kiesling, F. Meggendorfer, K. Unger, S. Hiesl, T. Forsthofer, A. Ishikawa, Y. Ahn, T. Ferber, I. Haide, G. Heine, C. -L. Hsu, A. Little, H. Nakazawa, M. Neu, L. Reuter, V. Savinov, Y. Unno, J. Yuan, Z. Xu

https://

My general experience from looking at a lot of RTL between work and open hardware stuff is that ASIC people seem to be more heavy users of advanced systemverilog features (structs, interfaces, etc) than FPGA people.

I know a lot of FPGA tools historically didn't have great support for these things but unless you're still using ISE or Vivado 2017 there's no excuse.

Anyone else see this trend too?

Development of BPM electronics for PIP-II at Fermilab

Shengli Liu (Fermilab, Batavia, USA), Nathan Eddy (Fermilab, Batavia, USA), A. Semenov (Fermilab, Batavia, USA), Brian Fellenz (Fermilab, Batavia, USA)

https://arxiv.org/abs/2509.15388

Rare view of my desk during video editing.

With appropriate beverage vessels.

ZynqParrot: A Scale-Down Approach to Cycle-Accurate, FPGA-Accelerated Co-Emulation

Daniel Ruelas-Petrisko, Farzam Gilani, Anoop Mysore Nataraja, Zoe Taylor, Michael Taylor

https://arxiv.org/abs/2509.20543

SpecMamba: Accelerating Mamba Inference on FPGA with Speculative Decoding

Linfeng Zhong, Songqiang Xu, Huifeng Wen, Tong Xie, Qingyu Guo, Yuan Wang, Meng Li

https://arxiv.org/abs/2509.19873

A Resource-Driven Approach for Implementing CNNs on FPGAs Using Adaptive IPs

Philippe Magalh\~aes (LabHC), Virginie Fresse (LabHC), Beno\^it Suffran (LabHC), Olivier Alata (LabHC)

https://arxiv.org/abs/2510.02990

Bridging Simulation and Silicon: A Study of RISC-V Hardware and FireSim Simulation

Atanu Barai, Kamalavasan Kamalakkannan, Patrick Diehl, Maxim Moraru, Jered Dominguez-Trujillo, Howard Pritchard, Nandakishore Santhi, Farzad Fatollahi-Fard, Galen Shipman

https://arxiv.org/abs/2509.18472

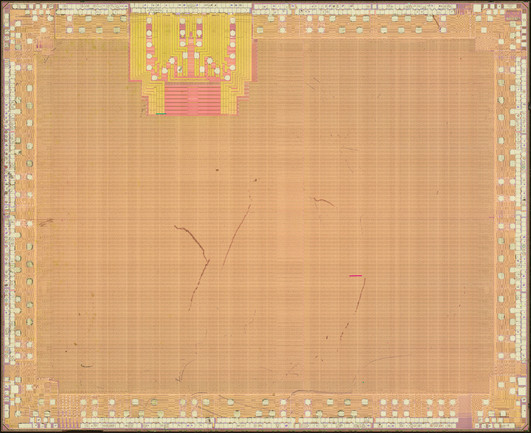

Xilinx XC6SLX25 (Samsung 45nm) from a previous decap run that I had to come back and finish because it was still stuck to the substrate.

A few light scratches in top passivation. These big BGAs need a lot of handling to peel back layers of fiberglass so acid can get in, which increases damage risk. Using fuming nitric usually you don't need that but I don't want it in my house :P

You can't see a whole lot here except the GTP. But if you compare this to the abstracted …

Open-source Stand-Alone Versatile Tensor Accelerator

Anthony Faure-Gignoux, Kevin Delmas, Adrien Gauffriau, Claire Pagetti

https://arxiv.org/abs/2509.19790 https://

Replaced article(s) found for cs.AR. https://arxiv.org/list/cs.AR/new

[1/1]:

- Holistic Optimization Framework for FPGA Accelerators

St\'ephane Pouget, Michael Lo, Louis-No\"el Pouchet, Jason Cong